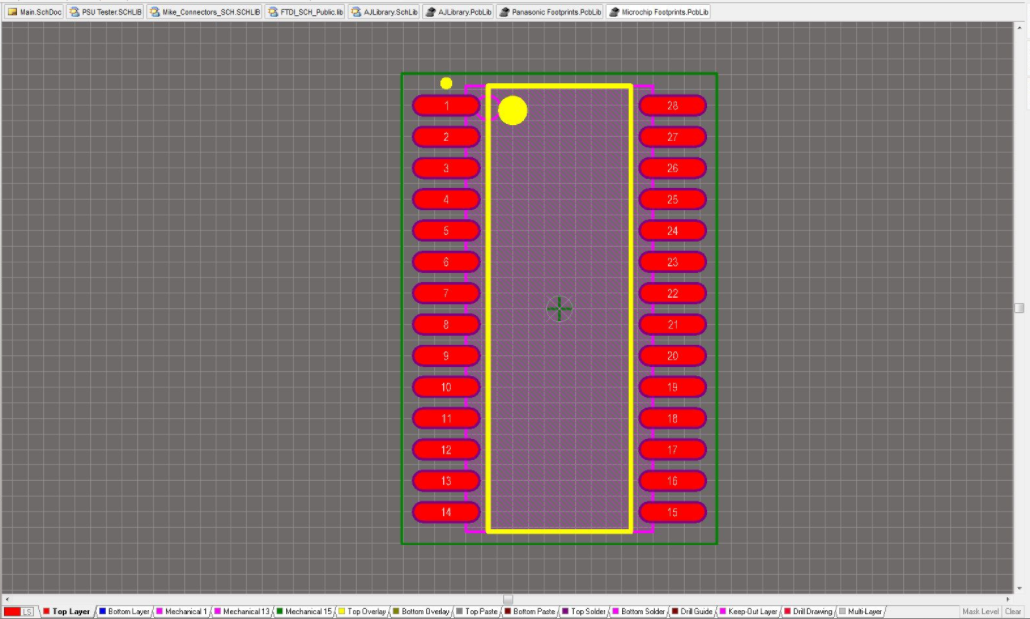

Add Jed file to PLD component: move the mouse to U1 (16v8), right-click, select component, and then left-click to call up the “component properties” dialog box. In order to make the PLD element simulate, it must be compiled in the circuit. In the circuit, i1-i3 is the input port of gal16v8, the port is 1 at high level, 0 at low level, io0-io7 is the output port, the output port is: the port outputs low level 0 when the LED light is on, and high level 1 when the LED light is off. Start Proteus and draw the circuit diagram.įigure 3 proteus simulation circuit diagram the LED display in the circuit adopts the display mode of LED lighting at low level. So far, the design of PLD file is completed. The output destination address of the Jed file. In the pop-up window, select 〔 export 〕 ] item, select. When drawing the PLD schematic diagram, input / output port (input: iPad, output: OPAD, input / output: iopad) components must be placed, and the pins specified by these components represent the pins of the target device.Īfter the I / O port component is placed, it must be numbered, and the pin number of the target device corresponding to the port component must be specified.Īfter completing the PLD schematic diagram, select / to compile and generate files of various formatsįigure 2 various files generated by compilation are opened. The PLD schematic design of Protel 99SE is the same as that of ordinary schematic, but there are several points to be notedĪfter the PLD meta diagram is generated, two PLD component libraries (PLDs) are automatically added to the schematic diagram_ Devices.lib 、PLD_ Symbols.lib )The components in these two libraries must be used to draw the circuit diagram of PLD. The input signal is the 2, 3 and 4 pins of the target component, the output signal is the 12-19 pins of the target component, and the 6-8 pins are the enable control terminal. The completed PLD schematic diagram is as follows:įigure 1 shows the schematic diagram of PLD, which is the PLD file of a 3-8 decoder. We use gal16v8 to design a 38 decoder which is commonly used in MCU system, and then observe the corresponding relationship between the input and output of the 38 decoder in gal16v8 in Proteus to complete the circuit simulation of PLD.įirstly, the PLD is designed with Protel 99SE.

#PROTEL 99SE FOOTPRINT LIBRARY SOFTWARE#

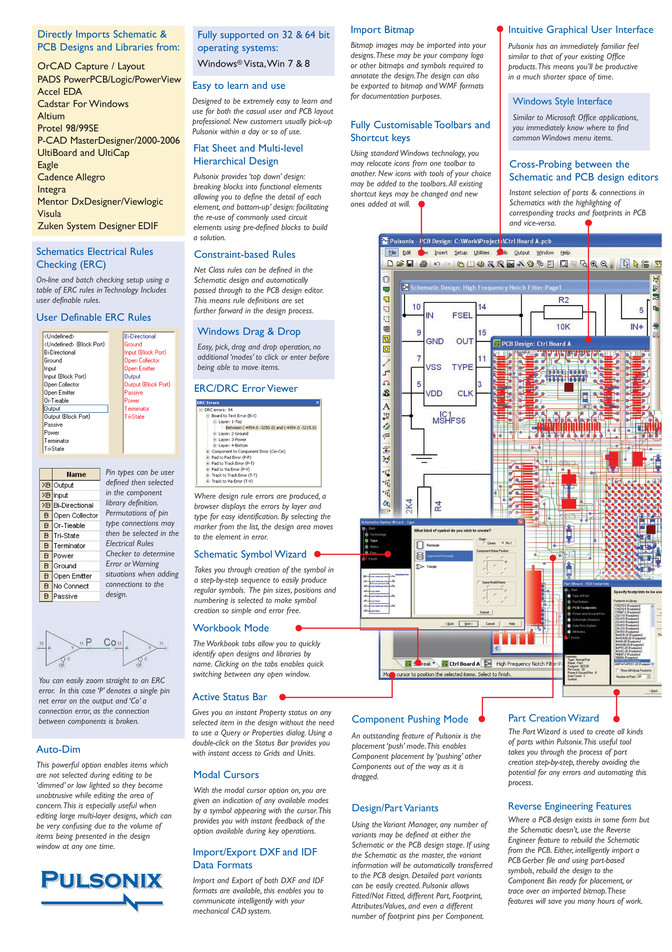

General PLD design software can only simulate the timing logic of PLD chip, while Proteus can simulate the circuit of PLD and simulate the actual operation of the designed PLD chip in the circuit. Users can use some development tools to process them, that is, to connect the elements in the chip according to the design requirements, so that they can complete the functions of a logic circuit or system, and become a programmable logic device that can be used in the system Application specific integrated circuit used in actual electronic system. A large number of basic logic elements, such as gates and triggers, are integrated on the chip in a certain arrangement. PLD (programmable logic device) is a semi-finished product of digital integrated circuit.

In fact, proteus can also simulate PLD circuit.

#PROTEL 99SE FOOTPRINT LIBRARY HOW TO#

But now we only pay attention to Proteus Simulation of MCU and how to debug with keil. You can also see the effect of input and output after running. It can be programmed directly on the virtual prototype EDA based on the schematic diagram, and realize the real-time debugging of software source level.

Compared with other tools, the biggest feature of this software is that it can simulate MCU. Proteus is a tool software from British company, which is widely used in the world.

0 kommentar(er)

0 kommentar(er)